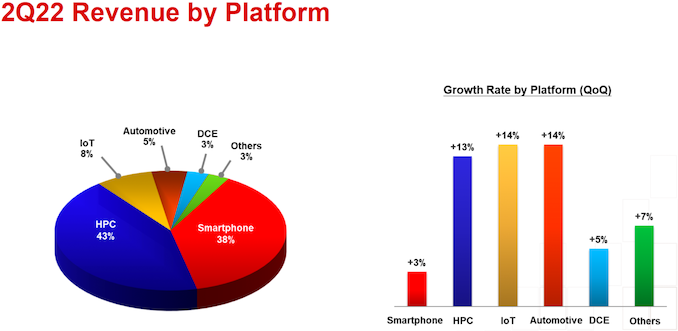

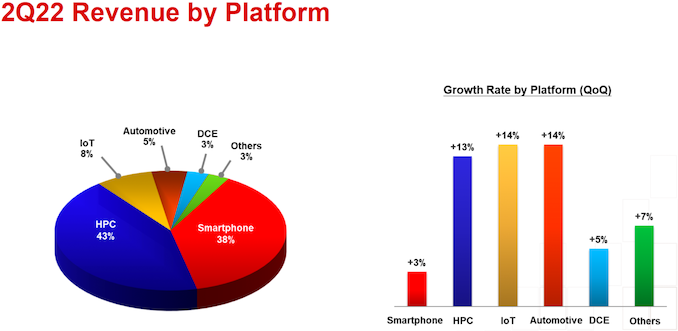

TSMC’s revenue this year is going to set an all-time record for the company, thanks to high demand for chips as well as increased prices that its customers are willing to pay for its services. While the company admits that demand for chips aimed at consumer devices is slowing, demand for 5G, AI, HPC, and automotive chips remains steady. In fact, TSMC’s main problem at present is getting more fab equipment, as ASML and other tool firms and reporting that demand for semiconductor production tools significantly exceeds supply.

Last week TSMC posted its financial results for the second quarter of 2022. The company’s revenue hit a record $18.2 billion, which was a year-over-year increase of 43.5%. The company revealed that while its sales were up 55% and 65.3% in April and May (respectively), its revenue in June was ‘only’ up 18.5% YoY, which indicates a slowdown in sales growth.

Demand for Client Devices Slowing

“Due to the softening device momentum in smartphone, PC and consumer end market segments, we observe the supply chain is already taking action and expect inventory level to reduce throughout the second half 2022,” said C.C. Wei, chief executive of TSMC, at the company’s earnings conference call.

While we can only speculate on this, it looks like some of TSMC’s customers reduced their orders for client-oriented chips after Russia started a full-scale war against Ukraine in late February. TSMC charges/recognizes revenue when it delivers chips/wafers to a client.

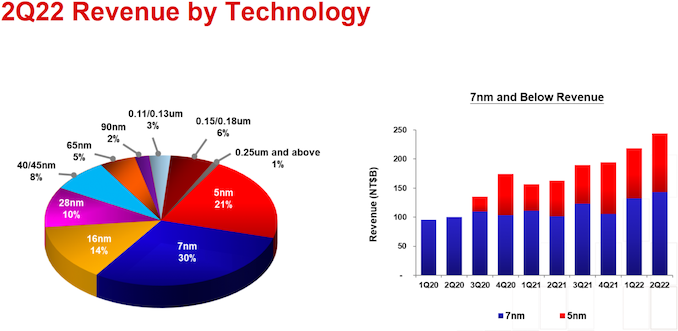

Production cycle for chips on modern process technologies is well over 60 days depending on complexity and the number of layers: N16 is ~60 days, N7 is 90+ days, N5 is probably well over 100 days. These nodes account for 65% of TSMC’s revenue. So, if clients started to wind down orders in March and April as they anticipated increasing inflation and uncertainty among the end user, the effect will be seen in June, which is what can be observed in TSMC’s reports.

TSMC admits that demand for client-oriented chips is softening, but demand for chips designed to support 5G, AI, and HPC applications still exceeds the company’s abilities to supply.

“While we observe softness in consumer end market segments, other end market segments such as data center and automotive-related remain steady,” said Wei. “We are able to reallocate our capacity to support these areas. Despite the ongoing inventory correction, our customers’ demand continues to exceed our ability to supply. We expect our capacity to remain tight throughout 2022 and our full year growth to be mid-30% in U.S. dollar terms.”

Advanced Nodes to Remain Growth Drivers, Expansions Getting Tougher

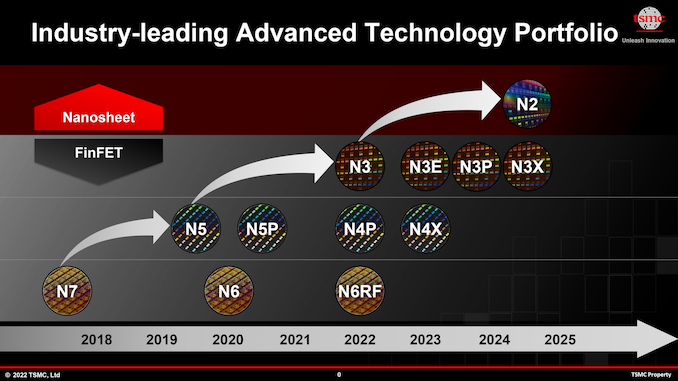

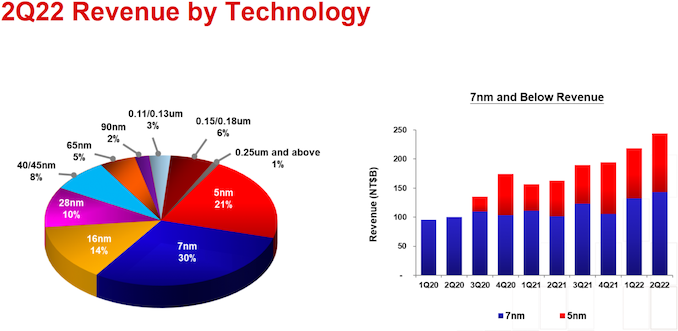

Over half of TSMC’s revenue (51%) comes from chips made using its advanced fabrication technologies (N7 and thinner nodes), which is not particularly surprising as TSMC is one of the only two contract foundries that offer such sophisticated manufacturing processes to clients.

These technologies will be among TSMC’s main growth drivers in the coming years, especially as more customers adopt N7 and more advanced technologies. But more N7/N6 and N5/N4 orders mean that TSMC will need to build more capacity for these nodes, as well as more capacity for N3 and subsequent nodes, which is why the company estimated that its CapEx this year would reach $40 billion – $44 billion.

“With the successful ramp of N5, N4P, N4X, and the upcoming ramp-up of N3, we will expand our customer product portfolio and increase our addressable market,” said the head of TSMC. “The macroeconomic uncertainty may persist into 2023, our technology leadership will continue to advance and support our growth. […] We believe the fundamental structural growth trajectory in the long-term semiconductor demand remains firmly in place. “

The world’s No. 1 contract maker of semiconductors also urges customers to migrate from older nodes to 28nm and specialty technologies as this will ensure capacity availability (as TSMC plans to expand capacity for 28 nm and specialty nodes by 50% by 2025) and denser designs potentially with more features.

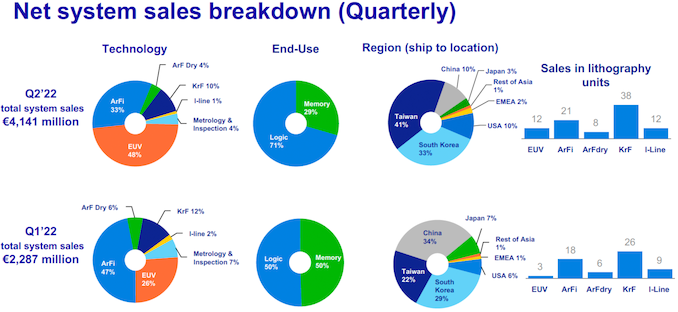

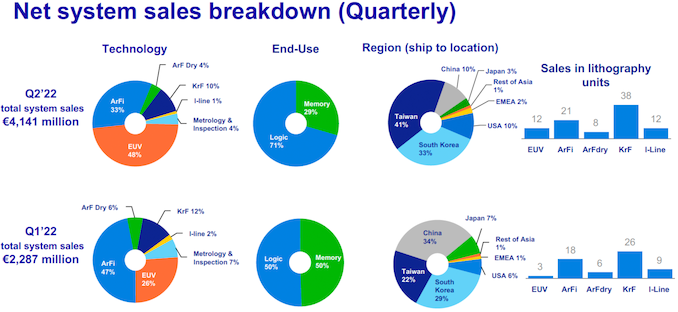

Building additional leading-edge, 28 nm, and specialty capacities not only requires massive investments, but TSMC needs to procure additional semiconductor production tools. Whether TSMC is building capacities for its brand-new N3 node or 28nm/specialty technologies, it should be noted that the company needs all kinds of lithography machines for them. An N3-capable fab needs dry litho tools, immersion litho scanners, and EUV-capable equipment. Without required number of dry and immersion scanners, an advanced EUV machine on its own will be useless. Meanwhile, lithography tools are not the only machinery that a fab needs.

Apparently, demand for fab equipment is so high that TSMC will not be able to spend its CapEx budget this year, and some purchases related to advanced (N7 and thinner) and mature nodes will be delayed into 2023. As a result, TSMC’s CapEx this year will be at a lower end of the company’s prediction (around $40 billion) not because it does not want to invest, but because it cannot invest in tools that are not available.

“Our suppliers have been facing greater challenges in their supply chains, which are extending tool delivery lead times for both advanced and mature nodes,” said Wei. “As a result, we expect some of our CapEx this year to be pushed out into 2023.”

ASML Confirms Record Quarterly Bookings

Meanwhile, ASML, the world’s largest producer of lithography tools, this week posted its Q2 2022 revenue of €5.431 billion, a 53% increase year-over-year. During the second quarter, the company supplied (recognized revenue) a total of 91 new lithography systems (up from 59 in Q2 2021), with 12 of those being EUV systems (up from 3 in Q2 2021).

What is perhaps more important is that ASML’s net bookings for new systems totaled €8.461 billion during the quarter, so the company’s bookings are higher than its quarterly sales. Meanwhile, ASML’s backlog now totals €33 billion and spans multiple years to come, which essentially is a yet another confirmation that it is extremely hard for companies like TSMC to get new tools.

The backlog for DUV machines is now at around 600 units and product order lead time for a new DUV scanner is now about two years. The backlog for EUV tools is well over 100 machines. Meanwhile, ASML says that PO lead time metrics is not exactly relevant since it faces supply chain and own production capacity issues, which means that its partners have to build additional capacity and ASML has to build additional capacity (which takes time) and only then it will be able to supply the tools ordered recently.

For the whole year 2022, ASML expects to ship 55 extreme ultraviolet (EUV) lithography scanners, but recognize revenue of 40 EUV systems valued at €6.40 billion (€160/$140 million per machine) because 15 EUV machines will be so-called fast shipments — a shipment process that skips some of the testing at ASML’s factory and then final testing and formal acceptance are performed at the customer site (which is why revenue acceptance gets deferred). The company also intends to supply 240 deep ultraviolet (DUV) litho tools this year. ASML expects its production capacity to total 60 EUV scanners and 375+ DUV tools in 2023.

Summary

While demand for chips aimed at client/consumer devices is getting softer due to rising inflation and geopolitical uncertainty, the global megatrends like 5G, AI, HPC, and autonomous vehicles are still there and these require loads of advanced system-on-chips, specialty processors, and not-so-advanced things like sensors. Therefore, TSMC is confident of strong demand for chips in the coming years.

But there is a problem with meeting that demand as TSMC is not the only company that is expanding its manufacturing capacity. ASML’s backlog now includes over 100 EUV scanners and around 600 DUV scanners — it will take years for the company to ship these machines. As a result, TSMC has problems with obtaining tools it needs to build additional capacity it needs. It is unclear whether the company has enough capacity to meet all of the potential demand from its largest customers on N3, N4, N5 nodes (Apple, MediaTek, AMD, NVIDIA, etc.), but, ultimately, tool shortages will affect all of its process technologies.

![]()

![]()

Source: AnandTech – TSMC and ASML: Demand for Chips Remains Strong, But Getting Fab Tools Is Hard